I²S Master Clock mit TTL Logik generieren

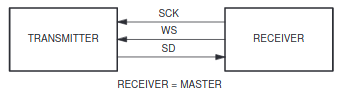

Digitale Audio ICs verwenden für die elektronische Übertragung der Audiodaten einen Datenbus, der im Jahre 1986 von der Firma Phillips als „Inter- Integrated Circuit Sound Bus“ – kurz I²S – spezifiziert wurde. Dieser Datenbus besteht in seiner ursprünglichen Form aus drei Leitungen: Einer Bitclock SCK/SCLK oder BCK/BCLK, einer Wordclock WS, WCLK oder LRCLK und schließlich die serielle Datenleitung SD, SDIN/SDOUT oder SDATA. Welche der genannten Abkürzungen in welcher Kombination verwendet wird könnte in der Praxis kaum inkonsistenter sein, im Regelfall wird jedoch schnell klar was gemeint ist.

Modernere Audiochips benötigen oft eine zusätzliche Masterclock, die jedoch nicht immer vorhanden ist. Unter bestimmten Voraussetzungen kann die Masterclock mit relativ wenig Aufwand mittels dreier Bauteile aus der Bitclock generiert werden.

I²S Bus Definition

Pic 3 verdeutlicht die Funtionen der Signale eines I²S Busses. Eine steigende Flanke der Bitclock veranlasst die Logik eines Receivers ein aktuelles Bit einzulesen, während eine fallende Flanke die Transceiverlogik das nächste Bit auf die Datenleitung setzen lässt. Die Übertragung erfolgt nach dem MSB- first Prinzip, das höchstwertige Bit im Datenwort wird also zuerst übertragen. Der Zustand der Wordclock signalisiert dabei, ob das Bit des folgenden SCK- Zyklus zum linken, oder zum rechten Kanal gehört.

Ein klassisches I²S Signal ist auf die Übertragung eines Stereosignals ausgelegt. Ein Zyklus der Wordclock deckt demnach jeweils ein Sample beider Audiokanäle ab, wodurch dieses Signal mit der Samplefrequenz f_{S} des Audiostreams taktet:

Gl. 1:

f_{WS} = f_{S}Die I²S Spezifikation beschränkt die Wortlänge eines Audiosamples zwar nicht, die Chips die mir bisher untergekommen sind arbeiten jedoch mit Wortlängen M von 32 Bit (von denen zumeist 16 bis 24 Bit tatsächlich genutzt werden). Daraus folgt, dass die Bitclock im Zeitraum einer Wordclockperiode 64 Zyklen vollführen muss. Mit der Kanalanzahl N folgt somit für die Frequenz der Bitclock im Allgemeinen:

Gl. 2:

f_{SCK} = M \cdot N \cdot f_{WS}Ein Stereosignal (N = 2) mit einer Auflösung M von 16 Bit (eingebettet in 32 Bit) mit einer Samplerate f_{S} von 48 Kilohertz erzeugt in einem I²S Stream demnach eine Bitclock mit der Frequenz:

Gl. 3:

f_{SCK} = 32 \cdot 2 \cdot 48 \text{ kHz} = 3072 \text{ kHz}I²S/TDM Masterclock

Wie bereits in der Einleitung erwähnt benötigen viele Audiochips für den Betrieb eine Zusätzliche Masterclock MCLK. Dies liegt zum einen daran, dass solche Chips relativ viel Logik wie Zustandsmaschinen beinhalten, die höher takten als der Audiodatenstrom. Zum anderen werden in mehrkanaligen Audiocodecs die Audiodaten per „Time Division Multiplex“ -Methode (TDM) übertragen, was letztlich eine höhere Datenrate zufolge hat. Diese Chips erfordern entweder zusätzliche Oszillatoren oder interne Phaselock Loops, oder eben ein Zusätzliches Taktsignal mit einer vielfachen Frequenz der I²S Bitclock.

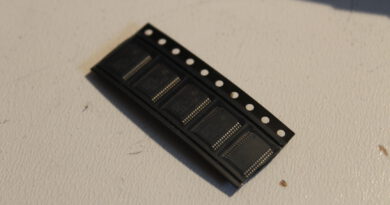

Als Beispiele für solche Audiochips kann ich kurzum den I²S DAC CS4344 von Cirrus Logic, den I²S – S/P-DIF Multipurpose Converter WM8804 von wolfson und den I²S Mono Class-D Amplifier TAS5720A von Texas Instruments nennen.

Während Prozessoren und Controller, die explizit für Audioanwendungen konzipiert sind in den meisten Fällen eine konfigurierbare Masterclock liefern, sucht man beispielsweise bei Embedded Modulen mit ARM Prozessoren vergeblich nach einer Masterclock. Auch der Raspberry Pi, in seinen verschiedenen Ausführungen, liefert lediglich Bitclock, Wordclock und serielle Audiodaten.

Workaround

Um I²S Chips mit Masterclock Input beispielsweise an einem Raspberry Pi zu betreiben, muss also die Masterclock seperat generiert werden. Versucht man dies unabhängig vom I²S Signaltakt führt dies in der Regel zu schlechter Signalqualität und Jitter, da durch Toleranzen immer eine Asynchronität zum I²S Takt vorhanden sein wird.

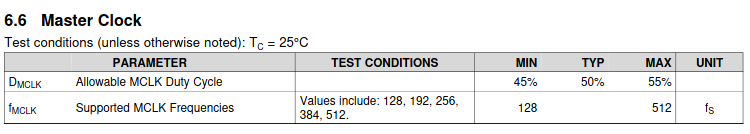

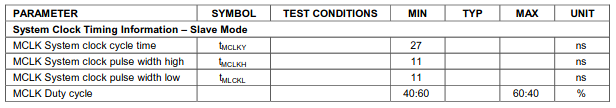

In Pic 4 und 5 ist zu sehen, dass die Masterclock beim TAS5720A und CS4344 als ein Vielfaches der Wordclock angegeben wird. Beim TAS5720 kann dieses Vielfache zwischen 128 und 512 liegen, der CS4344 unterstützt den Faktor 128 (Für Stereo, hier „Dual Signal Mode“ DSM) für Sampleraten 64, 88,2 und 96 Kilohertz. Der WM8804 hat eine komplexere interne PLL Logik und benötigt laut Datenblatt (Pic 6) nur eine minimale Zylkuszeit der Masterclock von 27 Nanosekunden, aus Versuchen mit diesem Chip kann ich aber sicher behaupten, dass dieser Chip mit einer Masterclock von 128 \cdot f_{WS} bei einer Samplerate von 44,1 Kilohertz hervorragend zurecht kommt.

Gleichung 3 verrät, dass die Bitclock eines I²S Streams bei einer Wortlänge M von 32 Bit die 64- fache Frequenz der Samplerate aufweist. Eine Verdoppelung dieser Frequenz kann demnach eine Masterclock liefern, die für bestimmte Betriebsmodi ausreicht.

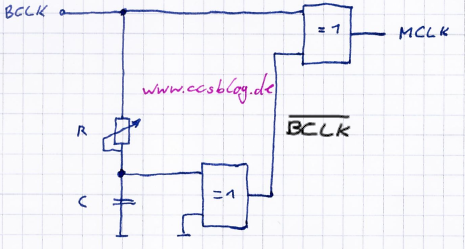

Anmerkung: Der Überstrich bei „\overline{BCLK}“ ist hier nicht (wie üblich) als logische Negierung gemeint, sondern soll lediglich einen Unterschied zur originalen Bitclock verdeutlichen. Beim Erstellen der Zeichnung hielt mich leider nichts davon ab, diese Unschönheit zu übersehen…

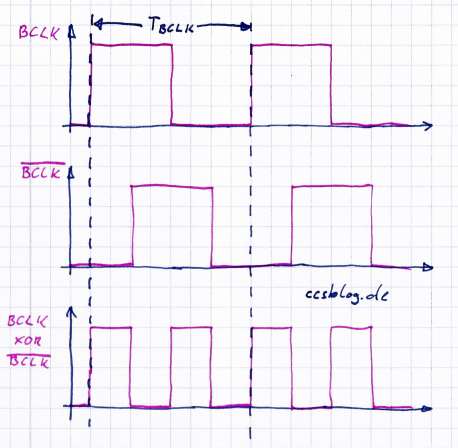

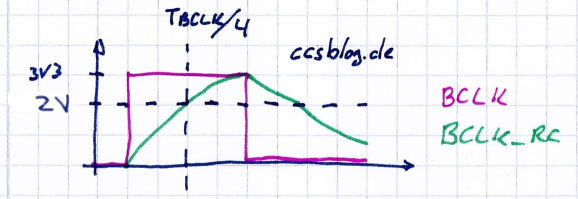

Pic 7 zeigt die Schaltung eines einfachen Frequenzverdopplers. Die XOR Glieder liefern eine logische ‚1‘, wenn an nur einem der beiden Eingänge eine logische ‚1‘ anliegt. Wenn beide Eingänge den gleichen logischen Pegel tragen liefert der Ausgang eine logische ‚0‘. Diese Antivalenz soll dazu genutzt werden, eine zeitlich verzögerte Form der Bitclock \overline{BCLK} mit dem originalen Signal zu vergleichen. Wird eine zeitliche Verzögerung von T_{BCLK}/4 eingestellt, sollte die Signalfrequenz am Ausgang doppelt so groß sein, wie die der Bitclock (siehe Pic 8).

Die zeitliche Verzögerung wird durch das RC- Glied erreicht, dessen Ausgang durch ein zusätzliches XOR- Glied gepuffert wird.

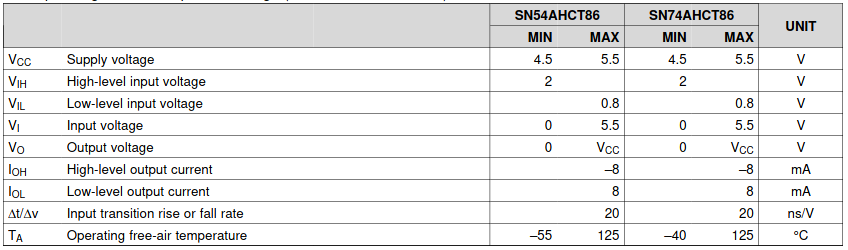

Als Logik IC verwende ich ein 4-fach XOR- Glied SN74HCT86 von Texas Instruments. Ein Blick in das Datenblatt gibt preis, dass ein Eingangssignal ab einem Pegel von 2 Volt als logische ‚1‘ interpretiert wird. Folglich muss das RC- Glied so dimensioniert werden, dass diese 2 Volt nach einer Viertel Bitclockperiode erreicht werden.

Eine Steigende Flanke der Bitclock löst einen Ladevorgang des RC- Gliedes aus, welcher sich beschreiben lässt durch:

Gl. 4:

v_{out} = v_{in} \left( 1 - e^{-\frac{t}{RC}} \right)Um das RC- Glied zu definieren wird Gleichung 4 nach R umgestellt:

Gl. 5:

\frac{v_{out}}{v_{in}} = 1 - e^{-\frac{t}{RC}}\\

\text{ }\\

e^{-\frac{t}{RC}} = 1 - \frac{v_{out}}{v_{in}}\\

\text{ }\\

-\frac{t}{RC} = \ln \left( 1 - \frac{v_{out}}{v_{in}} \right)\\

\text{ }\\

R = - \frac{t}{C \cdot \ln \left( 1 - \frac{v_{out}}{v_{in}} \right)}Die rechte Seite von Gleichung 5 enthält nun alle zu bestimmenden Variablen. Die Zeit t soll nach Pic 10 T_{BCLK}/4 betragen:

Gl. 6:

f_{BCLK} = 32 \cdot 2 \cdot f_S \text{ aus Gl. 2}\\

f_{BCLK} = 64 \cdot 48 \text{ kHz} = 3072 \text{ kHz}\\

T_{BCLK} = \frac{1}{f_{BCLK}} = 325,52 \text{ ns}\\

\frac{T_{BCLK}}{4} = 81,38 \text{ ns}Nach dieser Zeit soll die Ausgangsspannung des RC- Gliedes v_{out} 2 Volt betragen. Die Eingangsspannung v_{in} entspricht dem Pegel der Bitclock und wird mit 3,3 Volt angenommen. Als Kapazität C verwende ich einen Folienkondensator mit 330 Picofarad.

Setzt man diese Werte in Gleichung 5 ein, erhält man den Wert für den Widerstand R:

Gl. 7:

R = - \frac{81,38 \cdot 10^{-9} \text{ s}}{330 \cdot 10^{-12} \frac{\text{As}}{\text{V}} \ln \left( 1 - \frac{2 \text{ V}}{3,3 \text{ V}} \right)} = -\frac{81,38}{330 \cdot \ln \left( 1 - \frac{2}{3,3} \right)} \text{ k} \Omega = 264,72 \text{ } \OmegaAls Widerstand R wird daher ein Potentiometer mit einem Widerstand von 470 Ohm verwendet, dass auf den Zielwert justiert wird.

Versuch macht kluch

Genug der Theorie, sehen wir doch mal, ob sich die Schaltung auch in der Praxis umsetzen lässt.

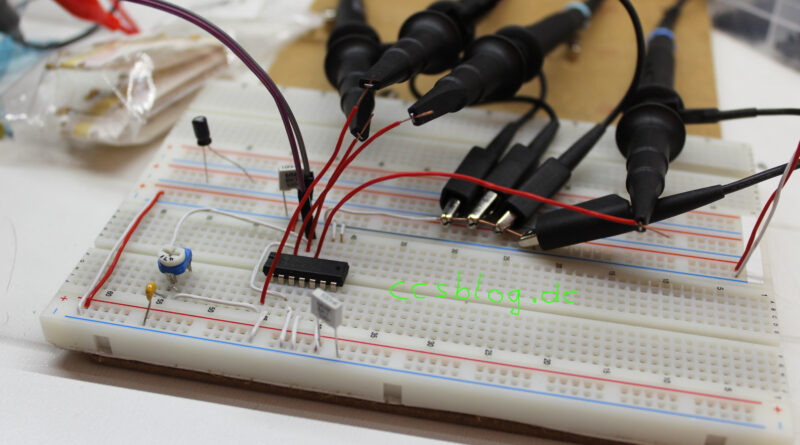

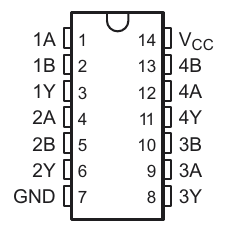

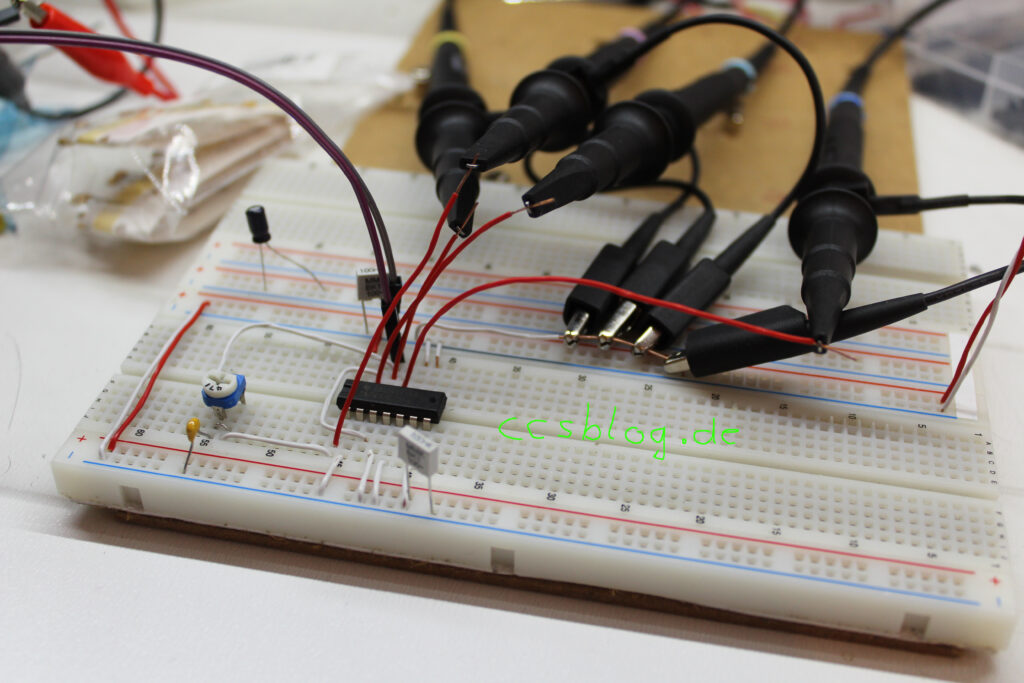

Pic 12 zeigt das Breadboard mit dem besprochenem IC und dem RC- Glied. Die Bitclock wird durch die violette Jumperleitung eingespeist. Auf dem Pinout in Pic 11 ist zu sehen, dass diese dem Eingang A des vierten XOR Gliedes des Chips zugeführt wird. von dort aus wird wird das Signal abgezweigt und dem Potentiometer zugeführt, welches zusammen mit dem Kondensator das RC- Glied bildet. Das dort generierte Tiefpasssignal wird auf Pin 1 des Chips geführt, welcher mit Eingang A des ersten XOR- Gliedes des Chips verbunden ist. Pin 2 wird mit Ground verbunden, was dazu führt, dass am Eingang B des ersten XOR- Gliedes 0 Volt anliegen und das Gatter als Puffer fungiert. Der Ausgang dieses Gatters liegt an Pin 3, welcher an Pin 13 dem Eingang B des vierten Gatters zugeführt. Damit wäre die Schaltung auch schon komplett, und die (hoffentlich funktionale) Masterclock kann an Pin 11 abgegriffen werden.

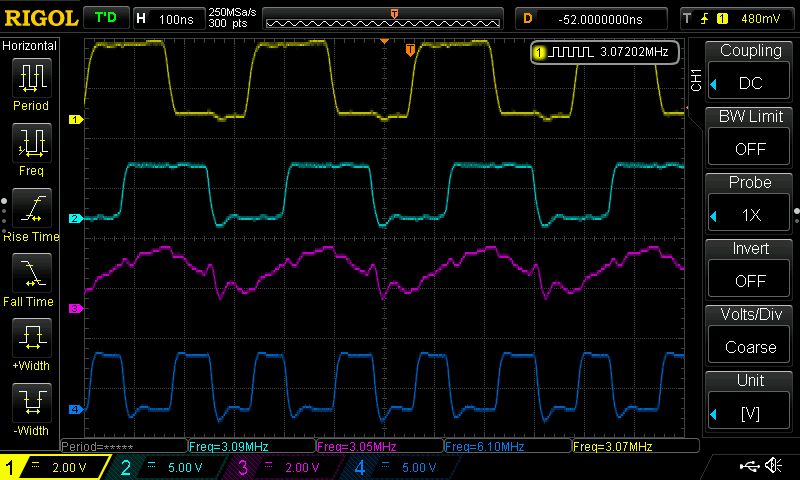

In Pin 12 ist zu sehen, dass ich mit meinem Oszilloskop vier Signale aufnehme. Kanal 1 (Gelb) greift hier die originale Bitclock auf, Kanal 2 (Cyan) die verzögerte Bitclock, Kanal 3 (Magenta) den Ausgang des RC- Gliedes und schließlich nimmt Kanal 4 (blau) die Masterclock am Ausgang der Schaltung auf.

Der Signalgenerator wird so eingestellt, dass dieser eine Bitclock für eine Samplefrequenz von 48 Kilohertz mit einem Pegel von 3,3 Volt simuliert.

Das so ein Breadboardaufbau alles andere als EMI- konform ist, lässt sich leicht an Kanal 3 (magenta) des in Pic 14 gezeigten Oszillographen sehen. Obwohl der Signalverlauf in seiner Grundform in etwa dem erwarteten Tiefpasssignal aus Pic 10 entspricht, ist eine deutliche Beeinflussung durch die Flanken der übrigen Signale zu erkennen. Dennoch reicht das Signal offenbar aus, um das erste XOR- Gatter des SN74AHCT86 Chips eine relativ saubere, verzögerte Version der Bitclock (Kanal 2 (cyan)) generieren zu lassen. Gut genug für Norddeutschland würde ich sagen 🙂

Kanal 4 zeigt in blau den Ausgang des vierten Gatters und damit die Antivalenz von Kanal 1 und 2. Das Resultat ist eine Masterclock mit der doppelten Frequenz der Bitclock.

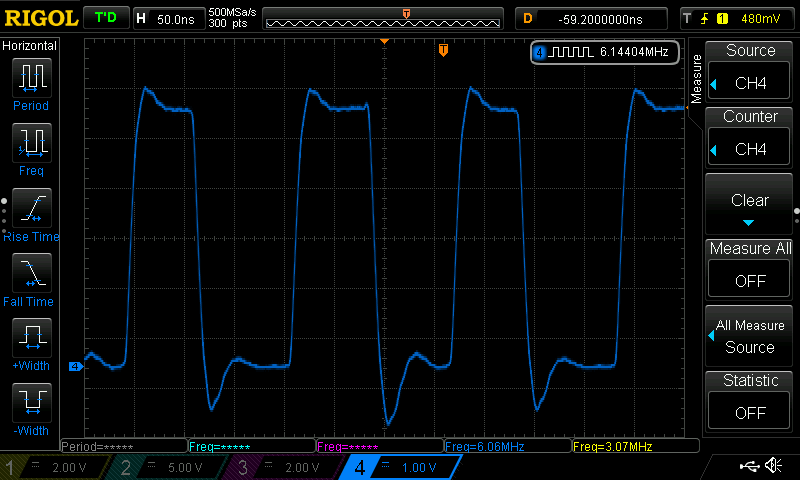

Bei genauerer Betrachtung der generierten Masterclock in Pic 15 fällt auf, dass das Signal zwei verschiedene Dutycycles aufweist. Mit anderen Worten heißt das, dass das zeitliche Verhältnis einer logischen ‚1‘ zu einer logischen ‚0‘ zwei unterschiedliche Werte annimmt. Das kann bei manchen Audiochips zu Problemen und Jitter führen. Bei den Überschwingern, die bei den Flanken auftreten handelt es sich um Fehlerfortpflanzungen des nicht idealen Breadboardaufbaus.

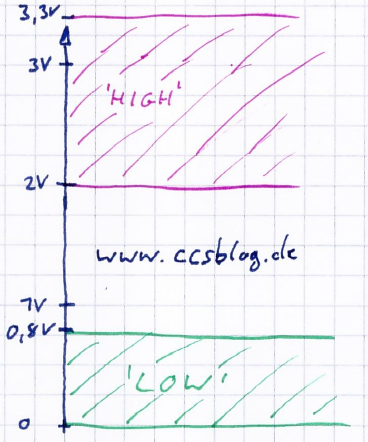

In Pic 16 habe ich die Schwellenwerte für ‚HIGH‘ und ‚LOW‘ Interpretation der Logikgatter aus Pic 9 grafisch dargestellt. Dadurch wird ersichtlich, dass mit der gleichbleibenden Zeitkonstanten \tau = RC des Tiefpasssignals kein regelmäßiger Dutycycle entstehen kann. Eine Möglichkeit zur Abhilfe wäre die Reduktion des Signalpegels auf 2,8 Volt, was aber nicht sehr praktikabel ist. Eine einfachere Möglichkeit ist die Feinjustierung des Widerstandes von R, wodurch die Dutycycles in einem gewissen Rahmen angeglichen werden können.

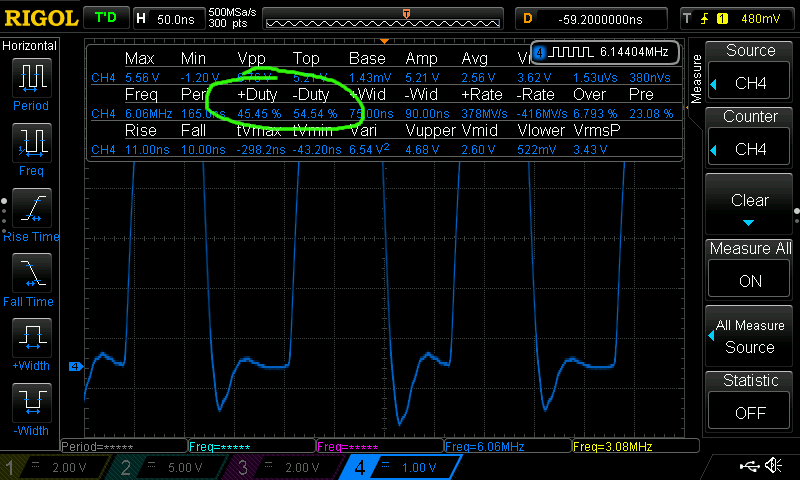

Pic 17 zeigt meine beste Angleichung der Dutycycles durch das Einstellen des Potentiometers. Die grün markierten Werte liegen im Rahmen von 10% zu einem idealen Dutycycle von 0,5. Dies ermöglicht die Verwendung dieser Masterclock in Verbindung mit einem TAS5720A Verstärker ICs, wenn man von den Werten im Datenblatt aus Pic 4 ausgeht.

Fazit

Dieser quick & dirty Versuch zeigt, dass für I²S Busse eine Masterclock mit 128- facher Samplefrequenz mit nur drei Bauteilen aus der Bitclock erzeugt werden kann.

In jedem Fall muss im Vorfeld das Datenblatt des Receiverchips untersucht werden, um sicher zu gehen, dass diese Frequenz mit der vorliegenden Samplerate verwendet werden kann. Prinzipiell ist es möglich, die hier behandelte Schaltung zu kaskadieren und somit Masterclocks mit 256- oder gar 512- facher Samplefrequenz zu generieren. Hierfür ist für jede Kaskade ein eigenes RC- Glied mit entsprechend kleinerer Zeitkonstante \tau zu bestimmen. Da bereits in diesem Versuch weder der Widerstand R mit 265 Ohm, noch die Kapazität C mit 330 Picofarad sehr groß dimensioniert sind, stellen die Toleranzen dieser Bauteile und die immer auftretenden parasitären Effekte einen unmittelbar limitierenden Faktor dar.

Weiter zeigt sich, dass die Schwellwerte des verwendeten Logik ICs einen direkten Einfluss auf die Gleichmäßigkeit des Dutycycles der erzeugten Masterclock haben. Es empfiehlt sich einen Logik- IC auszuwählen, dessen Schwellenwerte möglichst symmetrisch zur Hälfte der Auslenkung der originalen Bitclock sind, um aufwändige Pegelkorrekturen zu vermeiden.

Vor diesem Hintergrund bietet diese Methode eine praktikable Lösung und macht es beispielsweise möglich, Audio- Erweiterungsmodule für Raspberry- Pi Boards mit den Besagten Audiochips zu entwickeln.